低溫 Hybrid Bonding 顛覆 3D IC 堆疊極限:鎖與鑰 Cu/SiO₂ 結構引爆 HBM4 世代

- Kimi

- 2025年5月13日

- 讀畢需時 4 分鐘

一、Hybrid Bonding為何成為延續摩爾定律的必經之路?

在傳統摩爾微縮接近物理瓶頸、製程成本飆升之際,3D 異質整合被視為下一個黃金世代。Hybrid Bonding(混合接合)把銅-銅直通與氧化層-氧化層貼合合而為一,不依賴錫凸塊即可實現**<10 µm**、甚至次微米級的垂直互連;訊號路徑更短、RC 延遲更低,對 AI/HPC 所需的高頻寬記憶體(HBM)尤具吸引力。

Sony 在 2016 年首先在 CMOS 影像感測器量產,隨後 imec、TSMC、Intel、Samsung 等紛紛將技術推向 HPC 與記憶體晶堆。

二、「鎖與鑰」:IBM 奠基的設計思維

「鎖與鑰」Hybrid Bonding,一分鐘就懂

元件 | 角色 | 作用 |

頂層銅墊 / 銅柱 | 鎖(Lock) | 提供凸起結構,負責導電與固定 |

底層聚合物孔洞(PI 或 SiO₂) | 鑰(Key) | 尺寸略大、具彈性,包容並鎖住銅柱 |

先插入

兩片晶圓對準後,銅柱下壓至聚合物孔洞中,就像鑰匙插進鎖心。

再鎖死

在約 400 °C 熱壓時,聚合物暫時軟化、形變,讓銅柱完全貼合。

冷卻後聚合物回彈,銅柱被緊緊「卡」住,兼具機械強度與低電阻。

好處

可補償表面凹凸,避免硬碰硬造成空隙。

無需錫凸塊,互連 Pitch 可向 10 µm 甚至次微米推進。

一句話:用軟性聚合物「鑰匙孔」去包容銅「鎖」,在高溫下配合形變完成精準、牢靠且低電阻的 3D 垂直接合。

三、低溫之戰:金屬鈍化層讓 40 °C 也能鍵合

為什麼「金屬鈍化層」能把 Cu-Cu 接合溫度降到 40 °C?

隔氧又不隔銅

銅一接觸空氣就會迅速形成氧化層,這層「鏽」阻擋銅原子彼此擴散,所以傳統 Cu-Cu 接合得加熱到 300 – 400 °C 來打穿氧化層。

在銅表面先鍍 極薄(≈10 nm)的惰性金、銀、鈀或鈦,就像給銅穿一件防氧外套──氧氣進不去,但金屬薄膜裡的晶界仍是銅原子的「縫隙通道」。

室溫貼合、低溫退火

兩片晶圓對準後,在 室溫 ~40 °C 就能先「黏」在一起(初級鍵合);

之後只需 ≤150 °C 的短暫退火,銅原子沿晶界滲透到對面,完成緻密金屬連續體──完全避開高溫帶來的翹曲與應力。

低溫優勢一次到位

減壓縮 / 翹曲:溫差小,晶圓不容易變形。

保護 BEOL 元件:下游電路、介電層和先進晶體管都不再擔心 400 °C 熱預算。

尺寸無痛微縮:薄膜只是外衣,不改變銅本身的晶粒結構,Pitch 再縮也適用。

簡言之,金屬鈍化層=銅的防鏽薄膜 + 原子高速公路,讓 Cu-Cu 鍵合擺脫高溫束縛,40 °C 也能「貼得牢、貼得快」,成為混合接合攻克高層 HBM 堆疊的關鍵武器。

四、鑲嵌式銅與 DBI:從困境到靈感

鑲嵌式銅 (Damascene Cu) 與 DBI 的核心概念 — 用白話兩點搞懂

情境 | 簡單想像 | 關鍵突破 |

困境:鑲嵌銅表面凹陷 | 把銅填進矽氧化層的「壕溝」後,表面會微微凹下去 (約 20-50 nm)。兩片晶圓要貼合時,較硬的 SiO₂ 先碰到,凹陷的銅卻還沒接觸 → 良率低。 | |

靈感:DBI (Direct Bond Interconnect) | 先讓 氧化層對氧化層 在室溫「黏住」(像貼 OK 繃),再用 400 °C 退火。因為銅的熱膨脹比 SiO₂ 大,加熱時銅會「鼓起來」自動填平凹陷,最後形成銅-銅緊密接合。 | - 免高壓、免真空,製程時間短- 銅不用事先完全對齊,量產容忍度高 |

一句話總結:先黏氧化層、後讓銅膨脹補位,就把原本「銅凹陷難貼」的難題,變成高產能、高良率的 DBI 混合接合技術。

五、HBM4 為何一定要 Hybrid Bonding?

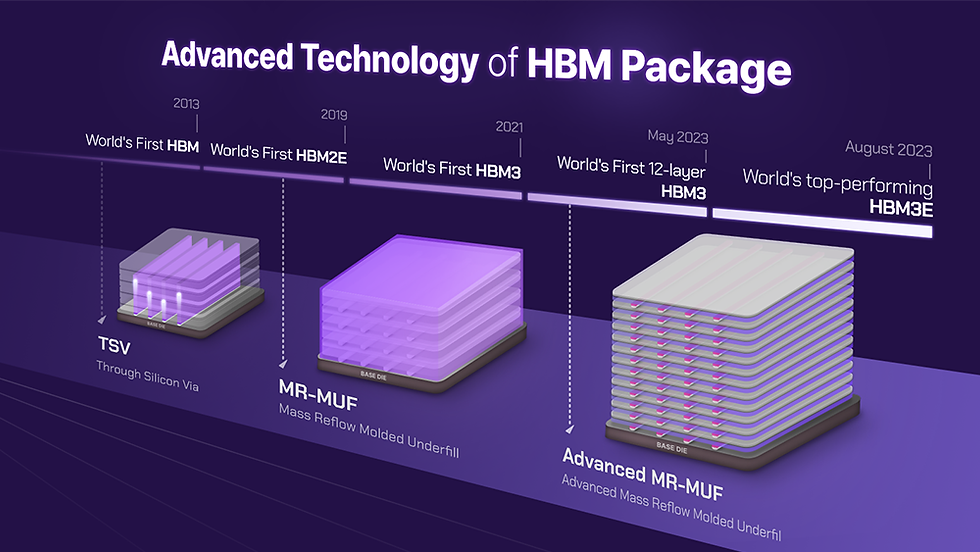

世代 | 疊層 | I/O 數 | 介面帶寬 | 主流接合 | 良率痛點 |

HBM3E | 12-Hi | 2048 | 1.5 TB/s | TC-Bump | 突破 12-Hi 難度高 |

HBM4 | 16-Hi | 4096 | 2 TB/s | Hybrid Bonding | Bump Pitch 已 <20 µm,變形、空隙暴增 |

HBM5 | 20-Hi | >4096 | >2 TB/s | Hybrid 必備 | TC-NCF 無法再縮 |

互連 Pitch:從 40-25 µm 逼進到 10 µm 以下

訊號完整性:鎖與鑰銅墊直聯,減少寄生 30-40 %

薄化需求:無凸塊,使堆疊厚度降至 775 µm(JEDEC 標準放寬後仍符合)

散熱:銅-銅連續性提升熱擴散,有利高功耗 AI GPU 模組

六、挑戰與前瞻:走向 Chiplet 生態系

對位精度 vs. 面板級產能:如何在 0.5 µm Pitch 仍保持 >90 % Bond Yield

熱管理:Fine-Pitch Bonding 會造成局部熱通量集中,需要整合 micro-channel 或 CVD 金剛石散熱片

設計工具鏈:EDA 必須同時考量電-熱-機耦合

Hybrid Bonding 已不只是封裝步驟,而是 架構設計的自由度。低溫「鎖與鑰」Cu/SiO₂ 解決了熱預算與機械應力兩大痛點,讓 HBM4 與更高層數記憶體堆疊成為現實,也替 Chiplet-Based 伺服器 CPU/GPU 大規模量產鋪路。

七、結語:Hybrid Bonding顛覆極限的新關鍵

低溫 Hybrid Bonding 用一把「鑰匙」打開了 3D IC 的下一道門。當銅-銅互連不再受溫度、凹陷與氧化束縛,當 Pitch 下探至奈米級、層數突破 20 Hi,未來的 AI 加速器、超大規模記憶體與異質 SoC 將以前所未有的密度與效率面世。對台灣供應鏈而言,誰能最快掌握低溫製程、對位控制與量產設備,誰就握有加速 HBM4 進化—乃至於整個 Chiplet 生態的 「主鑰匙」。